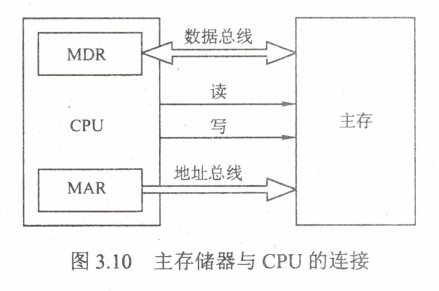

主存储器与CPU的连接

连接原理

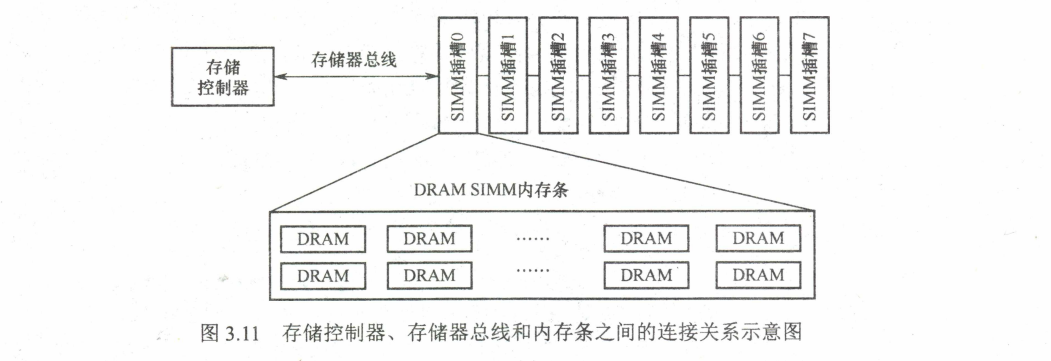

主存容量的扩展

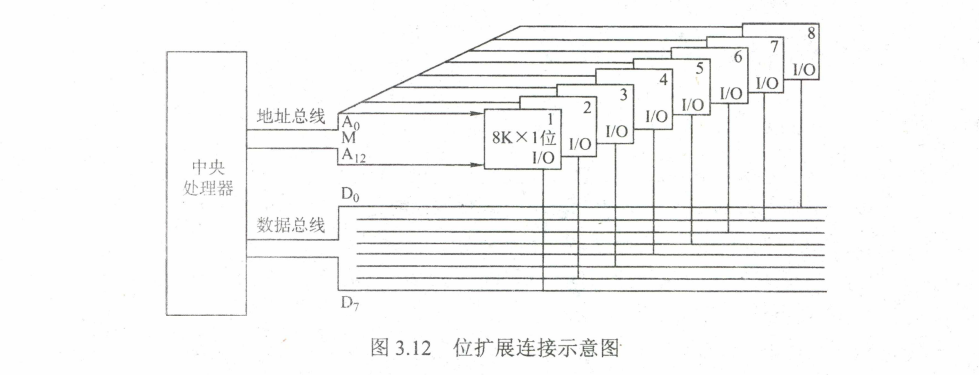

位扩展法

CPU的数据线数与存储芯片的数据位数不一定相等, 此时必须对存储芯片扩位。位扩展是将多个存储芯片的地址端、片选端和读写控制端相应并联,数据端分别引出。

仅采用位扩展时,各芯片连接地址线的方式相同,但连接数据线的方式不同,在某时刻选中所有的芯片,所以片选信号 $ \overline{CS} $ 要连接到所有芯片。

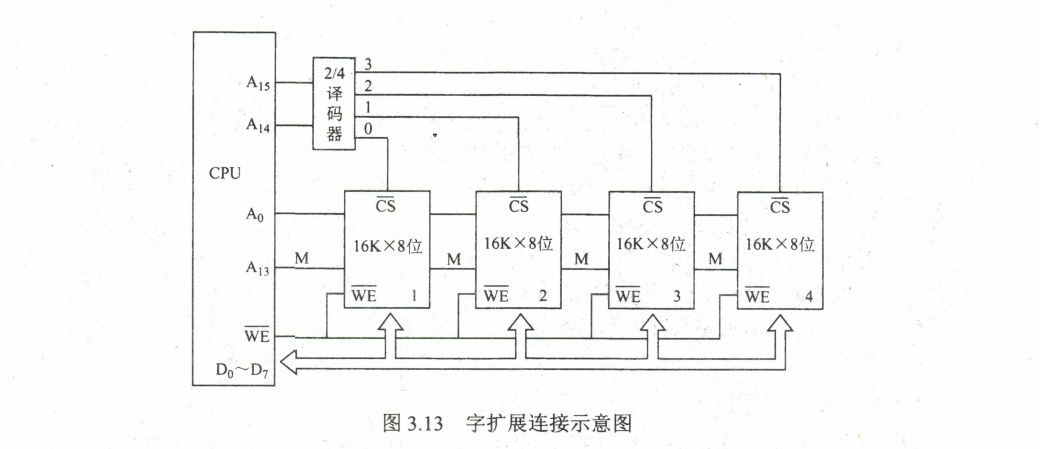

字扩展法

字扩展是指增加存储器中字的数量,而位数不变。字扩展将芯片的地址线、数据线、读写控制线相应并联,而由片选信号来区分各芯片的地址范围。

仅采用字扩展时,各芯片连接地址线的方式相同,连接数据线的方式也相同,但在某时刻只需选中部分芯片,所以通过片选信号 $ \overline{CS} $ 或采用译码器设计连接到相应的芯片。

字位同时扩展法

采用字位同时扩展时,各芯片连接地址线的方式相同,但连接数据线的方式不同,而且需要通过片选信号 $ \overline{CS} $ 或采用译码器设计连接到相应的芯片。

存储芯片的地址分配和片选

线选法

线选法用除片内寻址外的高位地址线直接(或经反相器)分别接至各个存储芯片的片选端。

优点: 不需要地址译码器,线路简单。

缺点: 地址空间不连续选片的地址线必须分时为低电平(否则不能工作),不能充分利用系统的存储器空间,造成地址资源的浪费。

译码片选法

译码片选法用除片内寻址外的高位地址线通过地址译码器芯片产生片选信号。

存储器与CPU的连接

合理选择存储芯片。

地址线的连接。

数据线的连接。

读/写命令线的连接

片选线的连接

片选有效信号与CPU的访存控制信号 $ \overline{MREQ} $(Memory Request, MREQ)有关,因为只有当CPU要求访存时,才要求选中存储芯片。若 CPU 访问 I/0,则MREO为高,表示不要求存储器工作。

补充

实际的主存容量不能代表MAR的位数

COPYRIGHT (c) OLENCER. ALL RIGHTS RESERVED.

- Title: 主存储器与CPU的连接

- Author: OLENCER.

- Created at : 2023-08-23 15:32:34

- Updated at : 2023-08-23 22:52:40

- Link: https://olencer.github.io/考研/408/计算机组成原理/主存储器与cpu的连接/

- License: This work is licensed under CC BY-NC-SA 4.0.

Comments