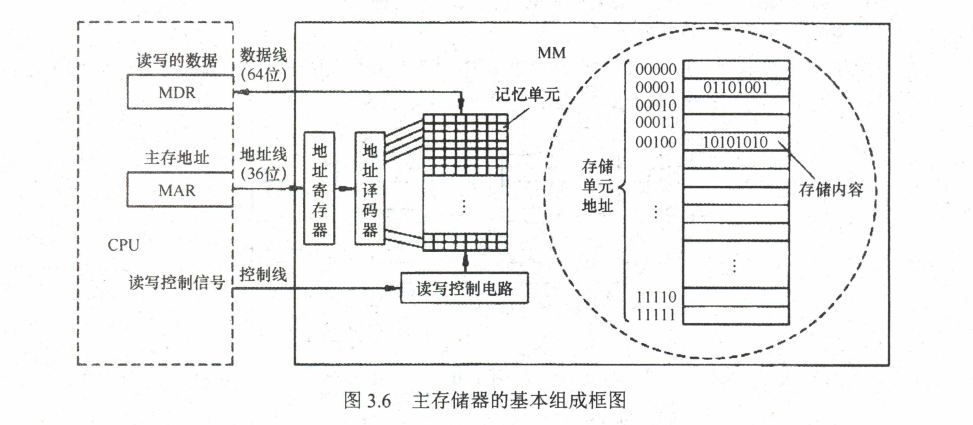

主存储器

主存储器的基本组成

主存储器(Main Memory, MM)

SRAM芯片和DRAM芯片

静态随机存储器(Staic Random Access Memory, SRAM)

工作原理

存储元是用双稳态触发器(六晶体管MOS), 非破坏性读出。

SRAM 的存取速度快, 但集成度低, 功耗较大, 价格昂贵, 一般用于高速缓冲存储器。

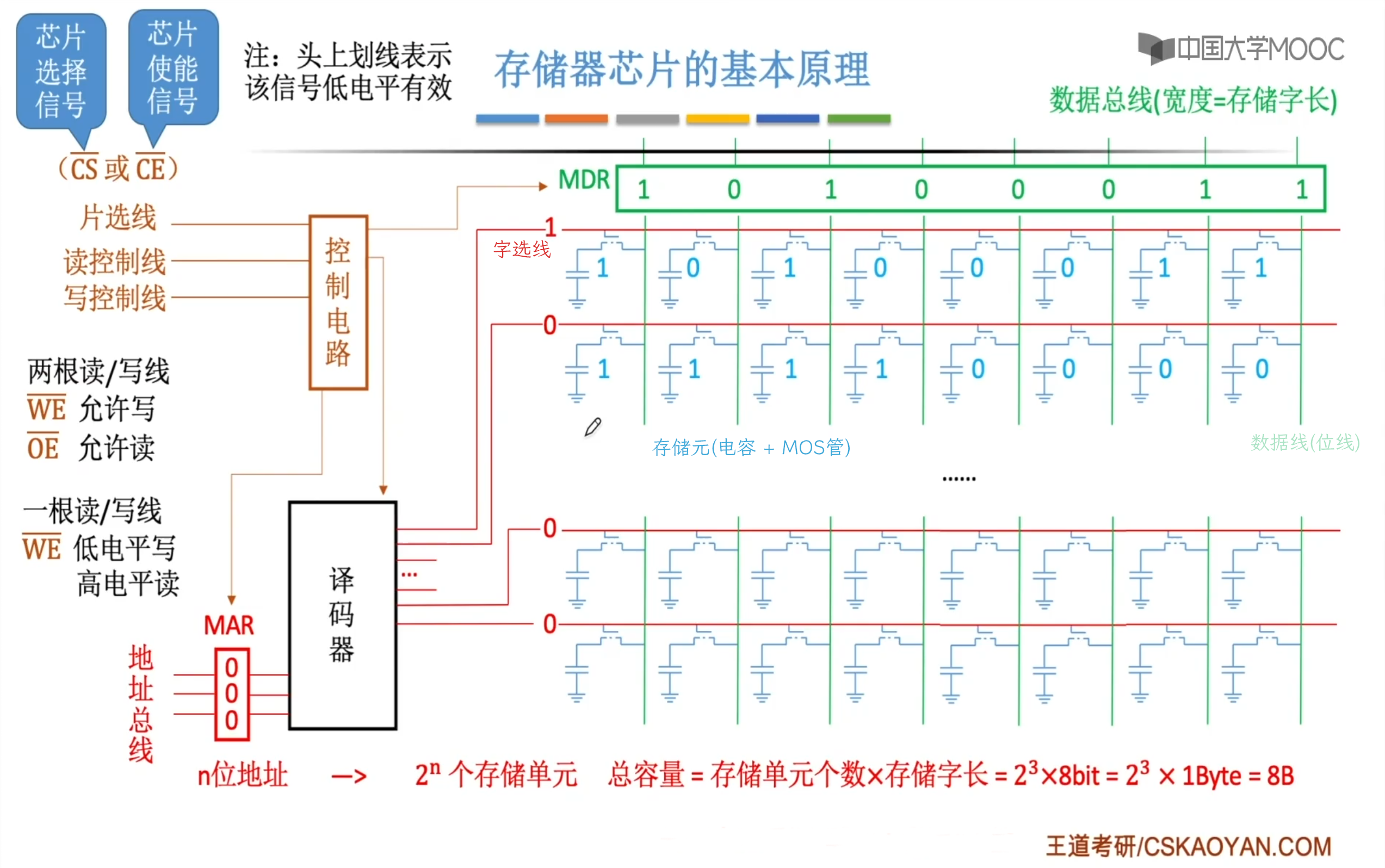

动态随机存储器(Dynamic Random Access Memory, DRAM)

工作原理

存储元是用栅极电容, DRAM的基本存储元通常只使用一个晶体管, 破坏性读出。

相对于SRAM来说, DRAM具有容易集成、密度高、位价低、容量大和功耗低等优点, 但DRAM的存取速度比SRAM的慢, 一般用于大容量的主存系统。

刷新

DRAM电容上的电荷一般只能维持1~2ms, 因此即使电源不断电, 信息也会自动消失。

为每隔一定时间必须刷新, 通常取2ms, 称为刷新周期。

以行为单位, 每次刷新一行存储单元。

集中刷新

指在一个刷新周期内, 利用一段固定的时间, 依次对存储器的所有行进行逐一再生, 在此期间停止对存储器的读写操作, 称为“死时间”, 又称访存“死区”。

优点是读写操作时不受刷新工作的影响。

缺点是在集中刷新期间(死区) 不能访问存储器。

分散刷新

把对每行的刷新分散到各个工作周期中。这样, 一个存储器的系统工作周期2分为两部分:前半部分用于正常读、写或保持:后半部分用于刷新。

优点是没有死区。

缺点是加长了系统的存取周期, 降低了整机的速度。

异步刷新

异步刷新是前两种方法的结合, 它既可缩短“死时间”, 又能充分利用最大刷新间隔为2ms的特点。具体做法是将刷新周期除以行数, 得到两次刷新操作之间的时间间隔t, 利用逻辑电路每隔时间t产生一次刷新请求。这样可以避免使CPU连续等待过长的时间, 而且减少了刷新次数, 从根本上提高了整机的工作效率。

注意

- 刷新对CPU是透明的, 即刷新不依赖于外部的访问。

- 动态RAM的刷新单位是行, 由芯片内部自行生成行地址。

- 刷新操作类似于读操作, 但又有所不同。刷新时不需要选片, 即整个存储器中的所有芯片同时被刷新。

地址线复用技术

行地址, 列地址分别送, 只用 n/2 根地址线。

行传送代替片选。

SRAM和DRAM的比较

| 特点 | SRAM | DRAM |

|---|---|---|

| 存储信息 | 触发器 | 电容 |

| 破坏性读出 | 非 | 是 |

| 需要刷新 | 不要 | 需要 |

| 送行列地址 | 同时送 | 分两次送 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 存储成本 | 高 | 低 |

| 主要用途 | 高速缓存 | 主机内存 |

同步动态随机存取内存(Synchronous Dynamic Random Access Memory, SDRAM)

只读存储器

掩模式只读存储器(Mask Read-Only Memory, MROM)

可编程只读存储器(Programmable Read-Only Memory, PROM)

写入一次后不可更改

可擦除可编程只读存储器(Erasable Programmable Read-Only Memory, EPROM)

Ultraviolet Rays Erasable Programmable Read-Only Memory, UVEPROM

紫外线擦除

Electrically Erasable Programmable Read-Only Memory, EEPROM($ E^{2}EPROM $)

电擦除

闪速存储器(Flash Memory)

固态硬盘 (Soild State Drives, SSD)

多模块存储器

单体多字存储器

单体多字系统的特点是存储器中只有一个存储体, 每个存储单元存储m个字, 总线宽度也为m个字。

一次并行读出 m 个字, 地址必须顺序排列并处于同一存储单元。

单体多字系统在一个存取周期内, 从同一地址取出m条指令, 然后将指令逐条送至 CPU 执行, 即每隔1/m存取周期, CPU向主存取一条指令。

优点: 这显然提高了单体存储器的工作速度。

缺点: 指令和数据在主存内必须是连续存放的, 一旦遇到转移指令, 或操作数不能连续存放, 这种方法的效果就不明显。

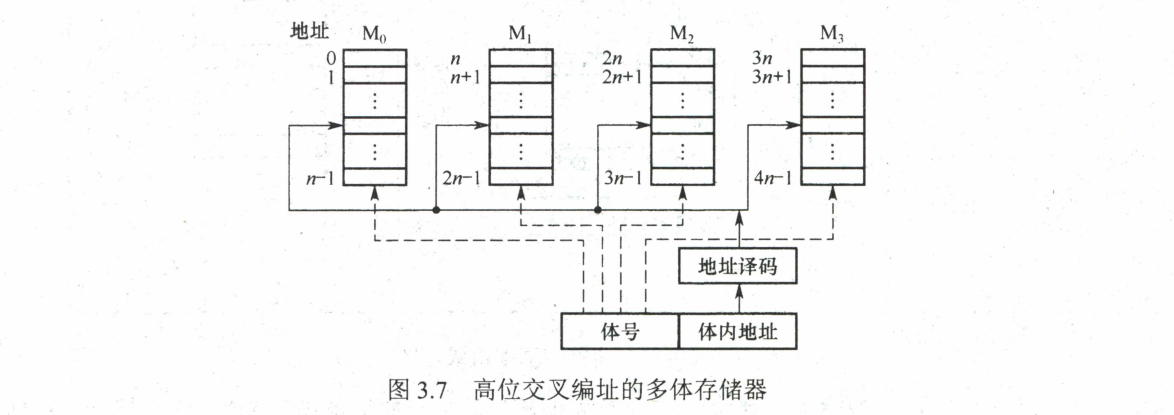

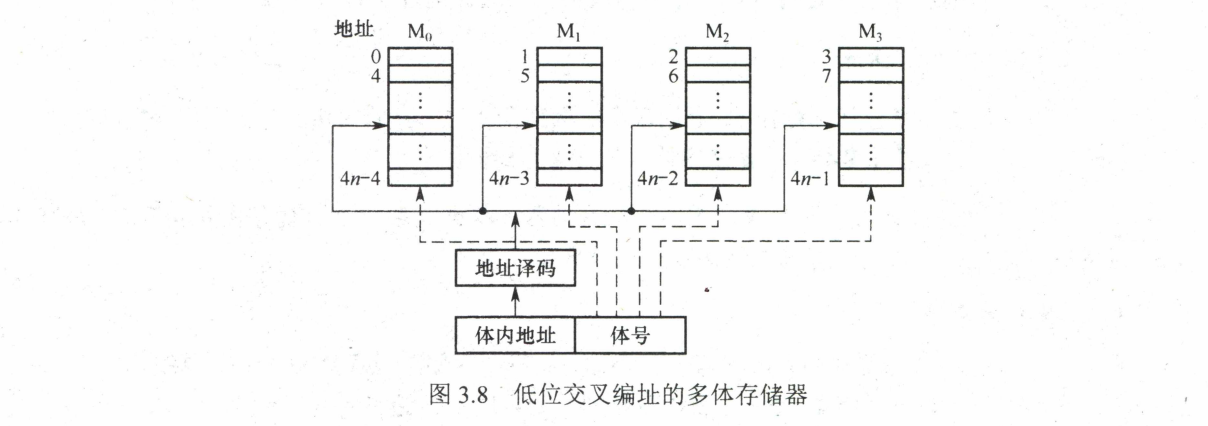

多体并行存储器

高位交叉编址(顺序方式)

模块内的地址是连续的, 存取方式仍是串行存取, 因此这种存储器仍是顺序存储器。

低位交叉编址(交叉方式)

设模块字长等于数据总线宽度, 模块存取一个字的存取周期为 $ T $, 总线传送周期为 $ r $, 为实现流水线方式存取, 存储器交叉模块数应大于等于

$$

m= T/r

$$

$ m $ 称为交叉存取度。

这样, 连续存取m个字所需的时间为

$$

t_{1} = T + (m - 1)r

$$

而顺序方式连续读取 $ m $ 个字所需的时间为$ t_{2} = mT $ 可见低位交叉存储器的带宽大大提高。

补充

只读存储器也可随机存取

随机存取与随机存取存储器 (RAM)不同, 只读存储器(ROM)也是随机存取的。支持随机存取的存储器并不一定是RAM。

访存冲突

给定的访存地址在相邻的n(模块数)次访问中出现在同一个存储模块内。

提高刷新存储器带宽(显示器)采用技术

- 采用高速DRAM芯片。

- 采用多体交叉存储结构。

- 刷新存储器至显示控制器的内部总线宽度加倍。

- 采用双端口存储器将刷新端口和更新端口分开。

多端口存储器、单体多字存储器和多体并行存储器的对比优缺点

多端口存储器:

缺点: 多端口存储器是对同一个存储体使用多套读写电路实现的, 扩大存储容量的难度显然(比多体结构的存储器)要大, 而且不能对多端口存储器的同一个存储单元同时执行多个写入操作。

单体多字存储器:

优点: (对于多端口存储器)每次读可以同时读出多个字的内容, 有利于提高存储器每个字的平均读写速度。

缺点: (对于多端口存储器)其灵活性不如多体单字结构的存储器, 还会多用到几个缓冲寄存器。

多体并行存储器:

优点: (对于多端口存储器)多体结构的存储器则允许在同一个存储周期对几个存储体执行写入操作。

刷新

刷新信号周期: 相邻两行位元之间刷新的时间间隔单元。

刷新周期: 从对整个存储器刷新结束时起,到对整个DRAM全部刷新一遍为止时间间隔。

COPYRIGHT (c) OLENCER. ALL RIGHTS RESERVED.

- Title: 主存储器

- Author: OLENCER.

- Created at : 2023-08-22 16:16:52

- Updated at : 2023-08-23 22:58:12

- Link: https://olencer.github.io/考研/408/计算机组成原理/主存储器/

- License: This work is licensed under CC BY-NC-SA 4.0.